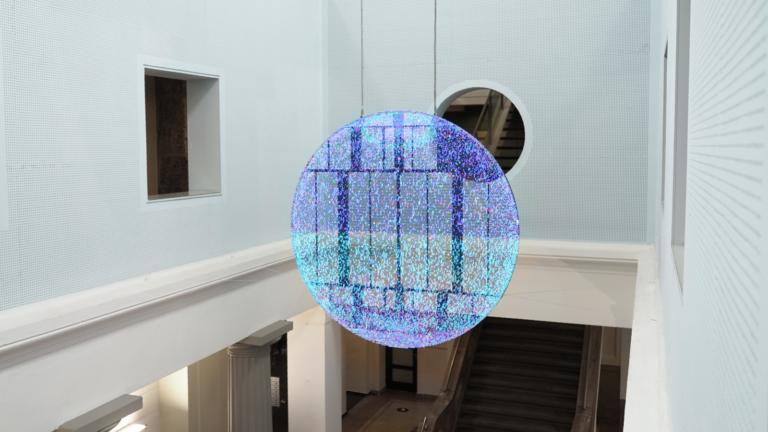

Created by Richard Vijgen, Hyperthread explores the aesthetics of parametric chip design through the lens of the Jacquard Loom. It is based on public domain microchips and emulators that perform different functions such as a cryptographic key generator, a general purpose CPU or a simple flipflop (the fundamental building blocks of a microchip).

Using open-source software (Verilog Hardware Description Language), the chips are translated from their coded instructions into three-dimensional graphical patterns. Instead of projecting these patterns on a silicon wafer at nanometer scale, they are translated into weaving instructions at millimeter scale. The result is a series of tapestries that reveal the different chips at a human scale, replacing interwoven silicon channels with coloured yarns. While the parametric patterns are not human-readable, they all share the same scale (1µm = 4mm) which allows for a comparison between simple and more complex chips. While the most complex chip (Gaussian Noise Generator) is 159×144 cm, the most simple chip (Flipflop) is only 18×16 cm. By blowing it up 4000 times, the tapestry series explores the spatial, tactile and aesthetic typologies of the common microchip.

The Jacquard Loom was not only a driver of the Industrial Revolution it also kickstarted the Information Age with the mechanical processing of information through the use of punchcards, a chain of cardboard cards punched with holes that determines which cords of the fabric should be raised with each pass of the shuttle. This proto-digital system used binary code (hole – no hole) to control the behaviour of individual threads in the loom (up or down) and allowed unskilled workers to weave complex patterns. While the binary principle (hole – no hole) still underpins modern day information technology, the threads in the loom also bear striking resemblance to the physical characteristics of the microcircuits that process digital information. Modern microchips can have up to 100 layers. Electrical current flows through channels of silicon and metal passing over and under other channels like a thread going up and down to produce a complex pattern. While the loom is made to produce patterns, in microchips they are a side effect, the result of a logical routing of channels to find the shortest path between A and B. In the early days of microchip design, these patterns were hand drawn on huge sheets of paper. Today most microchips are designed parametrically. A Digital Synthesis Flow translates code that defines the required functions of the circuit into a an efficient microchip lay-out. The result is a level of complexity way beyond human comprehension. It is also quite beautiful.

The work is based op public domain and opensource (historic) chip designs written in the Verilog Hardware Description Language. It uses the OpenLane Digital Synthesis flow to translate the hardware descriptions into GDSII chip layouts. These layouts are then translated to 2d graphics using custom python scripts and then into weaving instructions using the Nedgraphics Jacquard software. Woven with mixed yarns on a digital Dornier Jacquard with 6114 warp threads at Textiellab (NL).